Si consideramos que, en 1936, la primera calculadora binaria pesó más de 1 tonelada; la PC de la que nos valemos para leer este artículo es realmente un extraordinario logro de forma y función. Desde el desarrollo de los transistores, las mejoras de estos sistemas han acortado progresivamente los lapsos de tiempo entre una renovación y otra -al punto de sucederse actualmente en corto plazo. Tal es el caso de la nueva investigación realizada por Intel sobre los procesadores Tera-escalares.

La inmensa mayoría de computadoras actuales tiene procesadores de más de un núcleo. Realizamos nuestras tareas rápidamente y podemos cargar algunas aplicaciones y/o software de gran utilidad. Ahora, si nos plantean la posibilidad de tener procesadores de más de 80 núcleos, ¿que podríamos hacer? Mejor dicho, ¿qué no podríamos hacer? Quizá los requerimientos que necesitamos sean mínimos, pero determinados sectores de la población necesitan cada vez mayores velocidades en el procesamiento de datos para desarrollar tareas en paralelo.

En términos generales, la arquitectura Tera-escalar permitiría realizar teraFLOPS de operaciones en paralelo con terabytes de información -lo que ayudaría a que las aplicaciones visuales sean capaces de simular realidades basadas en conceptos físicos complejos. No obstante, todo desarrollo tecnológico presenta ciertas complicaciones. El presente caso no es la excepción.

PROGRAMACIÓN EN PARALELO

La técnica que da título a este acápite, empleada para aprovechar el rendimiento de un procesador de 80 núcleos, no fue diseñada junto con éste, sino que se elaboró a partir de las mejoras de un modelo antiguo cuyos resultados presentaban las siguientes dificultades:

1) Deficiencias en el consumo de energía ante el aumento de la frecuencia: la frecuencia es necesaria para que el procesador realice sus operaciones a alta velocidad. Un aumento no controlado de frecuencia puede generar pérdidas de energía en el sistema, haciéndolo más ineficiente.

2) Diferentes resultados utilizando el mismo programa: cuando se ejecuta un programa secuencial, el resultado obtenido siempre es el mismo. Las eventuales variaciones/diferencias dependerían únicamente de los valores de entrada asignados por el usuario o el computador (ejemplo: la calculadora al sumar dos números enteros). Al ejecutar un programa diseñado para funcionar en paralelo se corre el riesgo de obtener resultados diferentes debido a la dependencia de datos entre procesos u otros factores de programación (coordinación entre bloques, organización, patrones de ejecución, entre otros).

3) Paralelismo automático: los compiladores pueden especular, captar datos, reordenar instrucciones; para distribuir la carga entre los componentes de un sistema. Sin embargo, no es posible que creen un nuevo algoritmo para ejecuciones en paralelo, sobre la base de un algoritmo serial.

Ante estos problemas, las soluciones planteadas fueron:

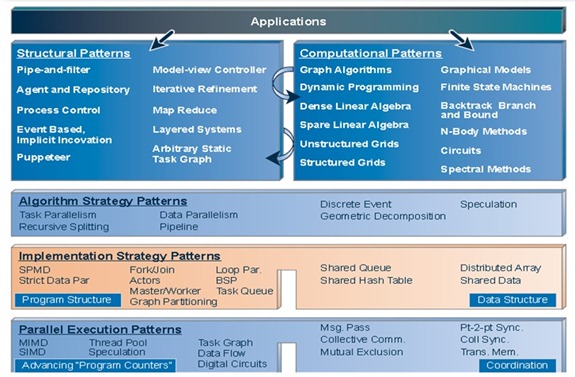

- Arquitectura de software: patrones de diseño.

- Alto nivel: organización de la aplicación.

- Nivel medio: cálculos específicos.

- Nivel bajo: estrategias de ejecución.

El cuadro anterior explica la estructura del patrón de lenguaje desarrollado por Intel, asi como sus patrones de diseño:

1. Muestra la organización general de la aplicación y como los elementos de la aplicación interactúan.

2. Muestra las distintas categorías de cálculos a realizar.

3. Cálculos recurrentes.

4. Codificación.

5. Coordinación entre bloques.

MEMORIAS

La velocidad con que el procesador se comunica con la memoria es un factor decisivo en la eficiencia del sistema. Para optimizar esta situación, se diseñaron las memorias caché, que funcionan como puentes entre la memoria principal del sistema (RAM) y el CPU. Estas memorias almacenan datos o instrucciones y al ir conectadas directamente al procesador, su velocidad de transmisión es mucho mayor. El reemplazo de la memoria RAM por memorias caché es prácticamente imposible, no por la complejidad de diseño, sino por el costo y la capacidad de almacenamiento.

Las características de memoria más comunes, consultadas y utilizadas para la fabricación/elección de estos componentes son las siguientes:

a) Ancho de banda.

b) Capacidad.

c) Tiempo de lectura de una palabra.

d) Energía por tiempo.

e) Energía por bit.

f) Tamaño (DIMMs).

g) Costo.

Actualmente, las memorias que abundan en el mercado son las DDR2, DDR3 y proximamente las DDR4. Si bien cada nueva versión trae mejoras en cuanto a velocidad y capacidad de almacenamiento, su principal problema es el siguiente:

En la imagen se muestra la disposición de los slots de memoria dentro de una computadora. La desventaja de esta organización es que en los puntos comunes se generan impedancias que tienen un gran efecto negativo en la transmisión de datos.

El siguiente gráfico presenta la curva del resultado de la transmisión de un bit de información. La línea azul es la respuesta teórica esperada, mientras que la línea roja es la respuesta real del sistema. Las grandes diferencias se deben al problema antes mencionado. Ante esto, los componentes internos de las memorias deben tener mayor tolerancia a esta variaciones; es por eso que se suele usar la tecnología CMOS, que tiene un máximo de 1V de tolerancia entre dos estados lógicos.

AHORRO DE ENERGÍA

El aumento de la frecuencia de un procesador no es la única causa de pérdidas de energía. Otro factor importante es el aumento de hardware en el procesador. En una arquitectura de 80 núcleos, este problema se incrementa considerablemente, ya que cada procesador debe contener unidades de procesamiento de datos y almacenamiento temporal (ALUs y memorias caché). La solución propuesta por Intel es la siguiente:

El añadir a ciertos núcleos aceleradores de tareas particulares ayuda a que la carga sea fácilmente distribuida. Esto disminuye los puntos donde la temperatura aumenta excesivamente debido a la alta frecuencia de trabajo. Este tipo de tecnología, usada también en procesadores Core2 Duo o subsiguientes, se denomina Hyperthreading.

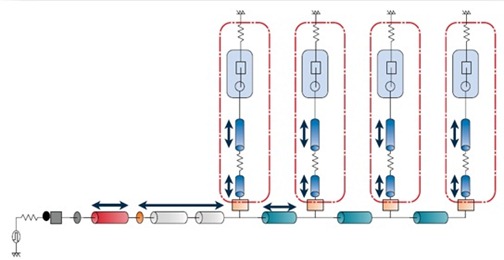

Finalmente, en la siguiente gráfica se muestra la organización interna de la arquitecura Tera-escalar. La sección aumentada corresponde a un solo núcleo y sus componentes internos.

NOTA ADICIONAL:

Hasta la fecha de escritura de este texto, el procesador de 80 núcleos era el más avanzado en modo de prueba. Hace ya dos semanas Intel empezó la investigación de un procesador de mayor eficiencia; sin embargo, la organización de componentes y los problemas que se presentaron fueron los mismos expuestos aqui.

Si les interesa conocer más sobre el funcionamiento del modelo, les recomiendo ver el video adjunto.

http://techresearch.intel.com/spaw2/uploads/files/Teraflops_research_chip-Long_version_final300K.wmv

Gabriel Jiménez

ENLACES RECOMENDADOS

Definición básica: http://es.wikipedia.org/wiki/FLOPS (en Wikipedia) y http://cxelectronico.blogspot.com/2010/07/arquitectura-de-computadoras-i.html (en Perú Electrónico).

Tecnología basada en el multinúcleo: http://www.intel.com/multi-core/index.htm?iid=tech_as+multi_head (en Intel) y http://www.eweekeurope.es/noticias/intel-sigue-evolucionando-parallel-studio-8052 (en eWeek Europe).

0 comentarios:

Publicar un comentario